#### Министерство образования и науки Самарской области Государственное бюджетное профессиональное образовательное учреждение Самарской области

# «САМАРСКИЙ ЭНЕРГЕТИЧЕСКИЙ КОЛЛЕДЖ» (ГБПОУ «СЭК»)

## ОП.08 МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ

Конспект лекций для студентов специальности 11.02.16 Монтаж, техническое обслуживание и ремонт электронных приборов и устройств

| Конспект лекций по дисциплине ОП.08 Микропроцессорные системы для студентов специальности 11.02.16. – Самара: ГБПОУ «СЭК». – 60 с. |

|------------------------------------------------------------------------------------------------------------------------------------|

| Издание содержит конспект лекций по дисциплине ОП.08 Микропроцессорные системы.                                                    |

|                                                                                                                                    |

| Замечания, предложения и пожелания направлять в ГБПОУ «СЭК» по                                                                     |

| адресу: 443001, г. Самара, ул. Самарская 205-А или по электронной почте info@sam-ek.ru                                             |

|                                                                                                                                    |

| ГБПОУ «СЭК»                                                                                                                        |

#### Раздел 1 Микропроцессорные системы. Основные понятия

#### Тема 1.1 Микропроцессорные системы (МПС). Виды и характеристики

1.Основные виды МПС и их особенности. Обобщенная структура МПС. Основные характеристики и параметры МПС. Краткая характеристика возможностей и применений микропроцессорных систем

Микропроцессорная система — цифровое устройство или цифровая система (система обработки данных, контроля и управления), построенная на базе одного или нескольких микропроцессоров. Программно-аппаратный принцип построения МПС — один из основных принципов их организации. Этот принцип заключается в том, что реализация целевого назначения МПС достигается не только аппаратными средствами, но и с помощью программного обеспечения.

Магистрально-модульный принцип организации микропроцессорной системы

Второй принцип, лежащий в основе организации микропроцессорных систем, — *магистрально-модульный принцип*. В соответствии с этим принципом основные структурные компоненты МПС выполняются в виде отдельных функционально законченных модулей, которые подключаются к единой внутрисистемной магистрали (шине).

Микропроцессорный модуль включает *микропроцессор*, *генератор тактовых импульсов* (ГТИ), а также, возможно, и другие устройства, например, *таймер*, *контроллер прерываний* и т.п.

В *подсистеме памяти* выделяют *модули ОЗУ*, предназначенных для хранения переменных и загружаемого извне программ, и *модули ПЗУ*, которые используются для хранения программ и констант.

В составе подсистемы ввода/вывода в простейшем случае выделяются адресуемые процессором буферные схемы и регистры — порты ввода/вывода. Они предназначены для связи с простыми внешними устройствами, такими как светодиодные индикаторы, переключатели и т.п. Более сложные модули подсистемы ввода/вывода, предназначенные для управления внешним интерфейсным оборудованием и реализации специальных функций ввода/вывода, строятся на основе портов ввод/вывод и называются адаптерами или контроллерами периферийных устройств. Наиболее сложными из модулей подсистемы ввода/вывода являются процессоры (сопроцессоры) ввода/вывода, которые работают по собственным программам, хранящимся в памяти, и по сути дела представляют собой отдельные микропроцессорные системы.

Основные классы микропроцессорных средств

Микропроцессор (МП) — функционально законченное программно-управляемое устройство, предназначенное для обработки данных и управления процессом этой обработки, выполненное в виде одной или нескольких микро-

схем. С точки зрения организации микропроцессорной системы – это ЦП, реализованный в виде одной или нескольких микросхем.

Микропроцессорная схема (МП схема) — интегральная микросхема (ИМС), выполняющая функцию МП или его части. По существу — это интегральная схема с процессорной организацией, разработанная для построения микропроцессорных систем. Микропроцессорные схемы относятся к особому классу микросхем, одной из особенностей которых является возможность программного управления ими с помощью определенного набора команд.

Mикро ЭВМ – ЭВМ, содержащая одну или несколько МП схем, микросхемы памяти (ПЗУ и ОЗУ), интерфейсов периферийных устройств, а также некоторые другие схемы (рис. 1).

Рис. 1 – Структура микроЭВМ

Микропроцессорный комплект (семейство, набор) (МПК) — совокупность МП и других микросхем, совместимых по конструктивно-технологическому исполнению и предназначенных для совместного применения при построении МП, микроЭВМ и микропроцессорных систем.

Однокристальная микроЭВМ – микроЭВМ, выполненная в виде одной интегральные схемы. Однокристальные микроЭВМ широко используются для управления различной аппаратурой и оборудованием, например в бытовых приборах.

Микроконтроллер — однокристальная микроЭВМ с небольшими вычислительными ресурсами и упрощенной системой команд, ориентированная на выполнение процедур логического управления различным оборудованием (а не на производство вычислений). Особенностью микроконтроллеров является расширенная реализация периферийных средств на кристалле.

Одноплатная микроЭВМ – микроЭВМ, выполненная в виде одной печатной платы и предназначенная для встраивания в различную аппаратуру. В отличие от однокристальной ЭВМ, размещая на одной плате несколько микросхем, можно получить микроЭВМ с достаточно большими вычислительными ресурсами.

*Микропроцессорные средства* – МПК, однокристальные (включая микроконтроллеры) и одноплатные микроЭВМ.

#### Тема 1.2.Организация функционирования МПС

1. Обобщенная структурная схема МПС. Алгоритм работы. Механизмы прерываний. Прямой доступ к памяти.

Прямой доступ к памяти (ПДП) является одним из способов обмена данными с ПУ. В этом режиме обмен данными между ПУ и памятью микропроцессорной системы происходит безучастия процессора. Обменом в режиме ПДП управляет не программа, выполняемая процессором, а внешнее по отношению к процессору специальное устройство, называемое контроллером ПДП (КПДП). ПДП используется для быстрого ввода/вывода блоков данных и разгрузки процессора от управления операциями ввода/вывода. Обмен блоками данных с помощью программно-управляемого обмена осуществляется относительно медленно, так как на обмен каждым байтом затрачивается несколько команд процессора. ПДП освобождает процессор от управления операциями ввода/вывода, позволяя тем самым

осуществлять параллельно во времени выполнение процессором программы и обмен данными между ПУ и памятью;

производить этот обмен со скоростью, ограниченной только пропускной способностью памяти или ПУ.

Таким образом, ПДП, разгружая процессор от обслуживания операций ввода/вывода, способствует возрастанию общей производительности микропроцессорной системы.

Для реализации режима ПДП необходимо обеспечить непосредственную связь контроллера ПДП и памяти микропроцессорной системы, т.е. специальный информационный канал, по которому осуществляется обмен в режиме ПДП, — канал ПДП. Для этой цели можно использовать специально выделенную магистраль, связывающую контроллер ПДП с памятью. Однако это приведет к значительному усложнению микропроцессорной системы в целом, особенно при подключении нескольких ПУ. Поэтому с целью сокращения количества линий в шинах микропроцессорной системы контроллер ПДП подключается к памяти посредством шин системной магистрали. При этом возникает проблема совместного использования шин системной магистрали процессором и контроллером ПДП. Можно выделить два основных способа ее решения:

реализация обмена в режиме ПДП с захватом цикла;

реализация обмена в режиме ПДП с блокировкой процессора. Режим ПДП с захватом цикла

Существует две разновидности прямого доступа к памяти с захватом цикла. Наиболее простой способ организации ПДП состоит в том, что для обмена используются те циклы процессора, в которых он не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора. Однако возникает необходимость вы-

деления таких циклов, чтобы не произошло временного перекрытия обмена ПДП с операциями обмена, инициируемыми процессором. В некоторых процессорах формируется специальный управляющий сигнал, указывающий циклы, в которых процессор не использует память. Если процессор не формирует такого сигнала, то для выделения свободных циклов необходимо применение в контроллере ПДП специальной схемы, что приводит к его усложнению. Применение этого способа организации ПДП не снижает производительности системы, но при этом обмен в режиме ПДП возможен только в случайные моменты времени одиночными словами.

Наиболее распространенным является *ПДП с захватом цикла и принуди- тельным отключением процессора от шин системной магистрали*. Для реализации такого режима ПДП системная магистраль дополняется двумя управляющими сигналами – *требование прямого доступа к памяти* HOLD и *предоставление прямого доступа к памяти* HLDA.

Управляющий сигнал HOLD формируется контроллером ПДП. Процессор, получив этот сигнал, приостанавливает выполнение текущей команды, не дожидаясь ее завершения, отключается от шин системной магистрали и выдает контроллеру ПДП управляющий сигнал HLDA. С этого момента все шины системной магистрали управляются контроллером ПДП. Контроллер ПДП, используя шины системной магистрали, осуществляет обмен одним словом данных с памятью и затем, сняв сигнал HOLD, возвращает управление системной магистралью процессору. Как только контроллер ПДП будет готов к обмену следующим словом данных, он вновь захватывает цикл процессора и т.д. В промежутках между захватами циклов контроллером ПДП процессор продолжает выполнять команды программы. Тем самым выполнение программы замедляется, но значительно в меньшей степени, чем при обмене в режиме прерывания.

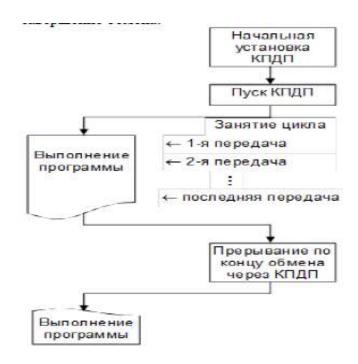

Передача блока данных с использованием ПДП предполагает выполнение определенной последовательности действий (рис. 2):

- 1. начальная установка (предварительная подготовка) контроллера ПДП;

- 2. запуск контроллера ПДП;

- 3. многократное занятие цикла процессора;

- 4. завершение обмена.

Рис. 2 – Передача блока данных с использованием ПДП

Программа используется только для начальной установки и пуска обмена через канал ПДП. После этого процессор может выполнять основную программу, которая не связана с обменом. Во время выполнения этой программы каждый раз при поступлении запроса на ПДП контроллер ПДП будет занимать цикл процессора и осуществлять передачу. После окончания обмена для передачи управления программе завершения обмена в режиме ПДП используется прерывание. Затем основная программа может быть продолжена.

Начальная подготовка к обмену в режиме ПДП состоит в выделении ПУ области памяти, используемой при обмене, и указании ее размера, т.е. количества записываемых в память или читаемых из памяти слов информации. Для этого контроллер ПДП имеет в своем составе регистр адреса и счетчик слов. Перед началом обмена с ПУ в режиме ПДП процессор должен выполнить

программу загрузки, которая обеспечивает запись в указанные регистры контроллера ПДП начального адреса выделенной ПУ области памяти и ее размера в словах заданной разрядности.

Запуск контроллера ПДП осуществляется командой вывода, по которой ПУ подключается к контроллеру ПДП. После команды пуска контроллера ПДП должна быть команда разрешения прерывания. В дальнейшем ввод блока данных через канал ПДП осуществляется без участия команд программы.

Когда ПУ подготовит слово данных, оно посылается в регистр данных контроллера. При этом каждое слово сопровождается управляющим сигналом ввод данных из ПУ, который обеспечивает запись слова данных в регистр данных контроллера и формирование сигнала требование прямого доступа к памяти HOLD. В ответ процессор формирует сигнал предоставление прямого доступа к памяти HLDA, после чего следующий машинный цикл зани-

мается под обмен. При этом осуществляется одна пересылка слова данных в ячейку памяти по адресу, находящемуся в регистре адреса контроллера. По сигналу HLDA контроллер выставляет на шины адреса и данных системной магистрали содержимое своих регистров адреса и данных соответственно.

Формируя управляющий сигнал MEMRW, контроллер ПДП обеспечивает запись слова данных из своего регистра данных в память.

После передачи каждого слова данных из содержимого счетчика слов контроллера вычитается 1, и когда оно становится равным 0, устанавливается запрос на прерывание, который поступает на соответствующий вход процессора. Процессор прерывает выполнение программы и передает управление подпрограмме обработки прерывания для завершения обмена.

Завершение обмена осуществляется путем отключения ПУ от контроллера ПДП командой вывода. По окончании обработки прерывания управление возвращается основной программе.

Если нет необходимости продолжать выполнение некоторой программы параллельно с передачей в режиме ПДП, то прерывание не используется. В течение обмена через канал ПДП процессор находится в цикле ожидания окончания передачи, опрашивая соответствующий разряд готовности регистра состояния контроллера ПДП по команде ввода. Как только процессор обнаружит готовность, он переходит к процедуре завершения обмена (шаг 4 рассмотренной выше последовательности), после чего выполнение программы продолжается.

Выше были рассмотрены только процесс подготовки контроллера ПДП и непосредственно передача данных в режиме ПДП. На практике любой сеанс обмена данными с ПУ в режиме ПДП всегда включает также и этап подготовки ПУ к обмену. На этом этапе процессор в режиме программно-управляемого обмена опрашивает состояние ПУ, проверяя его готовность к обмену, и посылает в ПУ команды, обеспечивающие его подготовку к обмену данными по каналу ПДП. Такая подготовка может сводиться, например, к перемещению головок на требуемую дорожку в НМД. Затем выполняется загрузка регистров контроллера ПДП, после чего начинается обмен данными в режиме ПДП.

Следует отметить, что использование в микропроцессорной системе обмена в режиме ПДП с захватом цикла требует от программиста очень ясного понимания процессов, происходящих в системе при выполнении программы, и четкой синхронизации процесса выполнения программы и ввода/выводапо каналу ПДП.

Режим ПДП с блокировкой процессора

Прямой доступ к памяти с блокировкой процессора отличается от режима ПДП с захватом цикла тем, что управление системной магистралью передается контроллеру ПДП не на время передачи одного слова, а на время обмена

блоком данных. Такой режим ПДП необходим в тех случаях, когда время между двумя сигналами *тебование прямого доступа к памяти* HOLD сопоставимо с циклом процессора. В этом случае процессор не успевает выполнить хотя бы одну команду между очередными операциями обмена в режиме ПДП.

В микропроцессорной системе можно использовать несколько ПУ, работающих в режиме ПДП. Предоставление таким ПУ шин системной магистрали для обмена данными производится на приоритетной основе. В этом случае приоритеты ПУ реализуются так же, как и при обмене данными в режиме прерывания. Как правило, для каждого ПУ используется своя пара управляющих сигналов требование прямого доступа к памяти HOLD и предоставление прямого доступа к памяти HLDA и отдельный канал в контроллере ПДП

#### Тема 1.3 Микропроцессоры (МП)

1. Классификация и характеристики МП. Понятие об архитектуре микропроцессора. Основные элементы архитектуры. Поколения МП.

**Микропроцессор**(МП) - это программно управляемое устройство, которое предназначено для обработки цифровой информации и управления процессом этой обработки и выполнено в виде одной или нескольких больших интегральных схем (БИС).

Понятие **большая интегральная схема**в настоящее время четко не определено. Ранее считалось, что к этому классу следует относить микросхемы, содержащие более 1000 элементов на кристалле. И действительно, в эти параметры укладывались первые микропроцессоры. Например, 4-разрядная процессорная секция микропроцессорного комплекта К584, выпускавшегося в конце 1970-х годов, содержала около 1500 элементов. Сейчас, когда микропроцессоры содержат десятки миллионов транзисторов и их количество непрерывно увеличивается, под БИС будем понимать функционально сложную интегральную схему.

**Микропроцессорная система**(МПС) представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, основу которой составляет микропроцессор.

Микропроцессор характеризуется большим количеством параметров и свойств, так как он является, с одной стороны, функционально сложным вычислительным устройством, а с другой - электронным прибором, изделием электронной промышленности. Как средство вычислительной техники он характеризуется прежде всего своей архитектурой, то есть совокупностью программно-аппаратных свойств, предоставляемых пользователю. Сюда относятся система команд, типы и форматы обрабатываемых данных, режимы адресации, количество и распределение регистров, принципы взаимодействия с оперативной памятью и внешними устройствами (характеристики сис-

темы прерываний, прямой доступ к памяти и т. д.). По своей архитектуре микропроцессоры разделяются на несколько типов (рис. 3).

**Универсальные микропроцессоры** предназначены для решения задач цифровой обработки различного типа информации от инженерных расчетов до работы с базами данных, не связанных жесткими ограничениями навремя выполнения задания. Этот класс микропроцессоров наиболее широко известен. К нему относятся такие известные микропроцессоры, как МП ряда Pentium фирмы Intel и МП семейства Athlon фирмы AMD.

Рис. 3. Классификация микропроцессоров

#### Характеристики универсальных микропроцессоров:

- разрядность: определяется максимальной разрядностью целочисленных данных, обрабатываемых за 1 такт, то есть фактически разрядностью арифметико-логического устройства (АЛУ);

- виды и форматы обрабатываемых данных;

- система команд, режимы адресации операндов;

- емкость прямоадресуемой оперативной памяти: определяется разрядностью шины адреса;

- частота внешней синхронизации. Для частоты синхронизации обычно указывается ее максимально возможное значение, при котором гарантируется работоспособность схемы. Для функционально сложных схем, к которым относятся и микропроцессоры, иногда указывают также минимально возможную частоту синхронизации. Уменьшение частоты ниже этого предела может привести к отказу схемы. В то же время в тех применениях МП, где не требуется высокое быстродействие, снижение частоты синхронизации одно из направлений энергосбережения. В ряде современных микропроцессоров при уменьшении частоты он переходит в <спящий режим>, при котором сохраняет свое состояние. Частота синхронизации в рамках одной архитектуры позволяет сравнить производительность микропроцессоров. Но разные архитектурные решения влияют на производительность гораздо больше, чем частота;

- производительность: определяется с помощью специальных тестов, при этом совокупность тестов подбирается таким образом, чтобы они по возможности покрывали различные характеристики микроархитектуры процессоров, влияющие на производительность.

Универсальные микропроцессоры принято разделять на CISC- иRISC-микропроцессоры. СISC-микропроцессоры (Completed Instruction Set Computing - вычисления с полной системой команд) имеют в своем составе весь классический набор команд с широко развитыми режимами адресации операндов. Именно к этому классу относятся, например, микро процессоры типа Pentium. В то же время RISC-микропроцессоры (reduced instruction set computing - вычисления с сокращенной системой команд) используют, как следует из определения, уменьшенное количество команд и режимов адресации. Здесь прежде всего следует выделить такие микропроцессоры, как Alpha 21х64, Power PC. Количество команд в системе команд - наиболее очевидное, но на сегодняшний день не самое главное различие в этих направлениях развития универсальных микропроцессоров. Другие различия мы будем рассматривать по мере изучения особенностей их архитектуры.

Однокристальные микроконтроллеры (ОМК или просто МК) предназначены для использования в системах промышленной и бытовой автоматики. Они представляют собой большие интегральные схемы, которые включают в себя все устройства, необходимые для реализации цифровой системы управления минимальной конфигурации: процессор (как правило, целочисленный), ЗУ команд, ЗУ данных, генератор тактовых сигналов, программируемые устройства для связи с внешней средой (контроллер прерывания, таймерысчетчики, разнообразные порты ввода/вывода), иногда аналого-цифровые и цифро-аналоговые преобразова- тели и т. д. В некоторых источниках этот класс микропроцессоров назы- вается однокристальными микро-ЭВМ (ОМЭВМ).

В настоящее время две трети всех производимых микропроцессорных БИС в мире составляют МП этого класса, причем почти две трети из них имеет разрядность, не превышающую 16 бит. К классу однокристальных микроконтроллеров прежде всего относятся микропроцессоры серии MCS-51 фирмы Intel и аналогичные микропроцессоры других производителей, архитектура которых де-факто стала стандартом.

# Отличительные особенности архитектуры однокристальных микроконтроллеров:

- физическое и логическое разделение памяти команд и памяти данных (гарвардская архитектура), в то время как в классической неймановской архитектуре программы и данные находятся в общем запоминающем устройстве и имеют одинаковый механизм доступа;

- упрощенная и ориентированная на задачи управления система команд: в МК, как правило, отсутствуют средства обработки данных с плавающей точкой, но в то же время в систему команд входят команды, ориентированные на эффективную работу с датчиками и исполнительными устройствами, например, команды обработки битовой информации;

- простейшие режимы адресации операндов.

**Основные характеристики микроконтроллеров**(в качестве примера численные значения представлены для MK-51):

- 1. Разрядность (8 бит).

- 2. Емкость внутренней памяти команд и памяти данных, возможности и пределы их расширения:

- внутренняя память команд 4 Кбайт (в среднем команда имеет длину 2 байта, таким образом, во внутренней памяти может быть размещена программа длиной около 2000 команд); возможность наращивания за счет подключения внешней памяти до 64 Кбайт;

- память данных на кристалле 128 байт (можно подключить внешнюю память общей емкостью до 64 Кбайт).

#### □ Тактовая частота:

- внешняя частота 12 МГц;

- частота машинного цикла 1 МГц.

- □ Возможности взаимодействия с внешними устройствами: количество и назначение портов ввода-вывода, характеристики системы прерывания, программная поддержка взаимодействия с внешними устройствами.

Наличие и характеристики встроенных аналого-цифровых преобразователей (АЦП) и цифро-аналоговых преобразователей (ЦАП) для упрощения согласования с датчиками и исполнительными устройствами системы управления.

Секционированные микропроцессоры (другие названия: микропрограммируемые и разрядно-модульные) - это микропроцессоры, предназначенные для построения специализированных процессоров. Они представляют собой микропроцессорные секции относительно небольшой (от 2 до 16) разрядности с пользовательским доступом к микропрограммному уровню управления и средствами для объединения нескольких секций.

Такая организация позволяет спроектировать процессор необходимой разрядности и со специализированной системой команд. Из-за своей малой разрядности микропроцессорные секции могут быть построены с использованием быстродействующих технологий. Совокупность всех этих факторов обеспечивает возможность создания процессора, наилучшим образом ориентированного на заданный класс алгоритмов как по системе команд и режимам адресации, так и по форматам данных.

Одним из первых комплектов секционированных микропроцессоров были МП БИС семейства Intel 3000. В нашей стране они выпускались в составе серии К589 и 585. Процессорные элементы этой серии представляли собой двухразрядный микропроцессор. Наиболее распространенным комплектом секционированных микропроцессоров является Am2900, основу которого составляют 4-разрядные секции. В нашей стране аналог этого комплекта выпускался в составе серии К1804. В состав комплекта входили следующие БИС:

- разрядное секционное АЛУ;

- блок ускоренного переноса;

- разрядное секционное АЛУ с аппаратной поддержкой умножения;

- типа схем микропрограммного управления;

- контроллер состояния и сдвига;

- контроллер приоритетных прерываний.

Основным недостатком микропроцессорных систем на базе секционированных микропроцессорных БИС явилась сложность проектирования, отладки и программирования систем на их основе. Использование специализированной системы команд приводило к несовместимости разрабатываемого ПО для различных микропроцессоров. Возможность создания оптимального по многим параметрам специализированного процессора требовала труда квалифицированных разработчиков на протяжении длительного времени. Однако бурное развитие электронных технологий привело к тому, что за время проектирования специализированного процессора разрабатывался универсальный микропроцессор, возможности которого перекрывали гипотетический выигрыш от проектирования специализированного устройства. Это привело к тому, что в настоящее время данный класс микропроцессорных БИС практически не используется.

**Процессоры цифровой обработки сигналов,** или **цифровые сигнальные процессоры**, представляют собой бурно развивающийся класс микропроцессоров, предназначенных для решения задач цифровой обработки сигналов обработки звуковых сигналов, изображений, распознавания образов и т. д. Они включают в себя многие черты однокристальных микро контроллеров: гарвардскую архитектуру, встроенную память команд и данных, развитые возможности работы с внешними устройствами. В то же время в них присутствуют черты и универсальных МП, особенно с RISC-архитектурой: конвейерная организация работы, программные и аппаратные средства для выполнения операций с плавающей запятой, аппаратная поддержка сложных специализированных вычислений, особенно умножения.

**Как электронное изделие** микропроцессор характеризуется рядом параметров, наиболее важными из которых являются следующие:

- 1. Требования к синхронизации: максимальная частота, стабильность.

- 2. Количество и номиналы источников питания, требования к их стабильности. В настоящее время существует тенденция к уменьшению напряжения питания, что сокращает тепловыделение схемы и ведет к повышению частоты ее работы. Если первые микропроцессоры работали при напряжении питания+-15B, то сейчас отдельные схемы используют источники менее 1 В.

- 3. **Мощность рассеяния** это мощность потерь в выходном каскаде схемы, превращающаяся в тепло и нагревающая выходные транзисторы. Иначе говоря, она характеризует показатель тепловыделения БИС, что во многом определяет требования к конструктивному оформлению микропро-

- цессорной системы. Эта характеристика особенно важна для встраиваемых МПС.

- 4. Уровни сигналов логического нуля и логической единицы, которые связаны с номиналами источников питания.

- 5. Тип корпуса позволяет оценить пригодность схемы для работы в тех или иных условиях, а также возможность использования новой БИС в качестве замены существующей на плате.

- 6. Температура окружающей среды, при которой может работать схема. Здесь выделяют два диапазона:

- коммерческий (0 °C ... +70°C);

расширенный (-40 °C ... +85 °C).

- Помехоустойчивость определяет способность схемы выполнять свои функции при наличии помех. Помехоустойчивость оценивается интенсивностью помех, при которых нарушение функций устройства еще не превышает допустимых пределов. Чем сильнее помеха, при которой устройство остается работоспособным, тем выше его помехоустойчивость.

- □ **Нагрузочная способность,** или коэффициент разветвления по выходу, определяется числом схем этой же серии, входы которых могут быть присоединены к выходу данной схемы без нарушения ее работоспособности. Чем выше нагрузочная способность, тем шире логические возможности схемы и тем меньше таких микросхем необходимо для построения сложного вычислительного устройства. Однако с увеличением этого коэффициента ухудшаются помехоустойчивость и быстродействие.

- □ **Надежность** это способность схемы сохранять свой уровень качества функционирования при установленных условиях за установленный период времени. Обычно характеризуется интенсивностью отказов (час-1) или средним временем наработки на отказ (час). В настоящее время этот параметр для больших интегральных схем обычно не указывается изготовителем. О надежности МП БИС можно судить по косвенным показателям, например, по приводимой разработчиками средств вычислительной техники надежности изделия в целом.

- □ Характеристики технологического процесса. Основной показатель здесь разрешающая способность процесса. В настоящее время она составляет 32 нм, то есть около 30 тыс. линий на 1 мм. Более совершенный технологический процесс позволяет создать микропроцессор, обладающий большими функциональными возможностями.

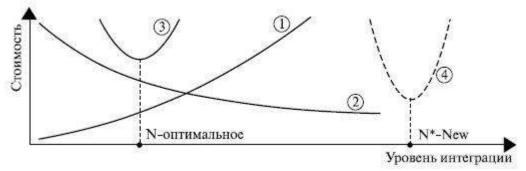

Рис. 4. Затраты на производство микропроцессорной системы

Затраты на изготовление устройств, использующих микропроцессорные БИС, представлены на рис. 1.2. Здесь:

- 1. затраты на изготовление БИС (чем больше степень интеграции элементов на кристалле, тем дороже обходится производство схемы);

- 2. затраты на сборку и наладку микропроцессорной системы (с увеличением функциональных возможностей МП потребуется меньше схем для создания МПС);

- 3. общая стоимость микропроцессорной системы, которая складывается из затрат (1) и (2). Она имеет некоторое оптимальное значение для данного уровня развития технологии;

- 4. переход на новую технологию (оптимальным будет уже другое количество элементов на кристалле, а общая стоимость изделия снижается).

В 1965 году Гордон Мур сформулировал гипотезу, известную в настоящее время как <закон Мура>, согласно которой каждые 1,5-2 года число транзисторов в расчете на одну интегральную схему будет удваиваться. Это обеспечивается непрерывным совершенствованием технологических процессов производства микросхем.

Наиболее развитая в технологическом отношении фирма Intel в жизненном цикле полупроводниковых технологий, создаваемых и применяемых в корпорации, выделяет шесть стадий.

Самая ранняя стадия проходит за пределами Intel - в университетских лабораториях и независимых исследовательских центрах, где ведутся поиски новых физических принципов и методов, которые могут стать основой научнотехнологического задела на годы вперед. Корпорация финансирует эти исследования.

На второй стадии исследователи Intel выбирают наиболее перспективные направления развития новых технологий. При этом обычно рассматривается 2-3 варианта решения.

Главная задача третьей стадии - полная черновая проработка новой технологии и демонстрация ее осуществимости.

После этого начинается четвертая стадия, главная цель которой - обеспечить достижение заданных значений таких ключевых технических и экономических показателей, как выход годных изделий, надежность, стоимость и неко-

торые другие. Завершение этапа подтверждается выпуском первой промышленной партии новых изделий.

Пятая стадия - промышленное освоение новой технологии. Эта проблема не менее сложна, чем разработка самой технологии, поскольку необычайно трудно в точности воспроизвести в условиях реального производства то, что было получено в лаборатории. Обычно именно здесь возникают задержки со сроками выпуска новых изделий, с достижением запланированного объема поставок и себестоимости продукции.

Последняя, шестая стадия жизненного цикла технологии (перед отказом от ее применения) - зрелость. Зрелая технология, подвергаясь определенному совершенствованию с целью повышения производительности оборудования и снижения себестоимости продукции, обеспечивает основные объемы производства. По мере внедрения новых, более совершенных технологий <старые> производства ликвидируются.

Но не сразу: сначала они переводятся на выпуск микросхем с меньшим быстродействием или с меньшим числом транзисторов, например, периферийных БИС.

#### Структура и особенности архитектуры микропроцессора Pentium 4

Микропроцессор Pentium 4 является завершающей моделью 32-разрядных микропроцессоров фирмы INTel с архитектурой IA-32. Основные особенности этого процессора:

- новая микроархитектура процессора NetBurst (пакетно-сетевая);

- новая системная шина FSB.

Микроархитектура процессора определяет реализацию его внутренней структуры, принципы выполнения поступающих команд, способы размещения и обработки данных. Микроархитектура NetBurst отличается от своих предшественников по целому ряду позиций:

- 1. Применена гарвардская структура с разделением потоков команд и данных.

- 2. Используется гиперконвейерная технология (Hyper-PIPelINed Technology) выполнения команд, при которой число ступеней конвейера достигает 31 (в Pentium III 11 ступеней). Таким образом, одновременно в процессе выполнения на разных стадиях реализации может находиться свыше 30 команд.

- 3. Используется динамическое выполнение команд (dynamic execution), построенное на трех базовых концепциях: предсказание переходов (branch prediction), динамический анализ потока данных (dynamic data flow analysis) и спекулятивное выполнение (OUT-oforder execution). Аналогичный механизм, названный Dynamic Execution, используется в МП Pentium III, однако в INTel Pentium 4 он улучшен.

- 4. Выполнение арифметических и логических операций происходит с удвоенной тактовой частотой процессора, что позволяет за один такт получить результаты для двух команд.

- 5. Кеш-память 2-го уровня емкостью 256 Кбайт размещается непосредственно на кристалле процессора, что позволяет сократить время выборки по сравнению с Pentuim III, где эта кэш-память располагается на отдельном кристалле в общем корпусе с процессором.

- 6. Значительно расширены возможности обработки чисел по принципу SIMD в новом блоке SSE-2.

Любой процессор архитектуры х86 обязательно оснащен процессорной шиной. Эта шина служит каналом связи между процессором и всеми остальными устройствами в компьютере: памятью, видеокартой, жестким диском и так далее. Так, классическая схема организации внешнего интерфейса процессора предполагает, что параллельная мультиплексированная процессорная шина, которую принято называть FSB (Front Side Bus), соединяет процессор (иногда два процессора или даже больше) и контроллер, обеспечивающий доступ к оперативной памяти и внешним устройствам. Этот контроллер обычно входит в состав северного моста набора системной логики (чипсета). Для ускорения обмена с памятью в Pentium 4 используется новая реализация системной шины, обеспечивающая обмен с эквивалентной частотой 400 МГц. Такая скорость достигается путем применения нового типа сверхбыстродействующей двухканальной памяти типа RDRAM и специальной микросхемы MCH (Memory ConTRoller Hub), реализующей 4 канала передачи данных. При тактовой частоте каждого канала 100 МГц обеспечивается общая частота обмена, эквивалентная 400 МГц. Шина включает 64-разрядную двунаправленную шину данных, дающую пропускную способность в 3,2 Гбайт/с, и 36-разрядную шину адреса (33 адресных линии А35-А3 и 8 линий выбора байтов ВЕ7-ВЕ0), что позволяет адресовать физическую память емкостью до 64 Гбайт. Именно учетверенная результирующая частота передачи данных является одним из главных предметов гордости разработчиков Pentium 4. Однако для многочисленных мелких запросов, где данные в большинстве своем умещаются в одну 64-байтную порцию (и, соответственно, не используются возможности многоканальной передачи), важнее именно частота тактирования. Последние модели Pentium 4 работают на частоте системной шины 150 МГц, что обеспечивает эквивалентную частоту FSB в 600 МГц и пропускную способность в 4,8 Гбайт/с.

Полученная по системной шине информация сохраняется в кэш-памяти 2-го уровня (L2) емкостью 256 Кбайт, общей для команд и данных, которая размещается непосредственно на кристалле МП. Ширина шины, по которой идет обмен данными между кэш-памятью L2 и процессором, составляет 256 бит (32 байта), а ее тактовая частота совпадает с тактовой частотой ядра процессора.

Гарвардская внутренняя структура реализуется на уровне кэш-памяти 1-го уровня (L1) путем разделения потоков команд и данных. Кэш-память данных 1-го уровня имеет емкость 8 Кбайт. Вместо кэш-памяти команд 1-го уровня в Pentium 4 используется кэш-память для декодированных команд (микрокоманд). Execution TRace Cache - это название и одновременно способ реализации L1-кэша инструкций в архитектуре NetBurst. Смысловое содержание этого термина можно перевести как "кэш трассировки выполняемых микрокоманд". В Execution TRace Cache хранятся микрокоманды (?ops), которые были получены в результате декодирования входного потока инструкций исполняемого кода и готовы для передачи на выполнение конвейеру. Емкость Execution TRace Cache составляет 12 Кбайт.

После заполнения кэш-памяти микрокоманд практически любая команда будет храниться в ней в декодированном виде. Поэтому при поступлении очередной команды блок трассировки выбирает из этой кэшпамяти необходимые микрокоманды, обеспечивающие ее выполнение.

Если в потоке команд оказывается команда условного перехода, то включается механизм предсказания ветвления, который формирует адрес следующей выбираемой команды до того, как будет определено условие выполнения перехода.

После формирования потоков микрокоманд производится выделение регистров, необходимых для выполнения декодированных команд.

Эта процедура реализуется блоком распределения регистров. Он выделяет для каждого указанного в команде логического регистра (регистра цлочисленных операндов EAX, EBX и т. д., регистра операндов с плавающей точкой ST0-ST7 или регистра блоков MMX, SSE) один из 128 физических регистров, входящих в состав блоков регистров замещения (БР3) целочисленного блока микропроцессора и блока обработки чисел с плавающей точкой. Эта процедура позволяет минимизировать конфликты в конвейерах и выполнять команды, использующие одни и те же логические регистры, одновременно или с изменением их последовательности.

Ступени распределения/переименования конвейера могут выпустить три микрокоманды за такт на следующую ступень конвейера.

Выбранные микрокоманды размещаются в очереди микрокоманд. В ней содержатся микрокоманды, реализующие выполнение до 120 поступивших и декодированных команд, которые затем направляются в исполнительные устройства. Отметим, что в процессорах Pentium III в очереди находятся микрокоманды для 40 поступивших команд. Значительное увеличение числа команд, стоящих в очереди, позволяет более эффективно организовать поток их исполнения, изменяя последовательность выполнения команд и выделяя команды, которые могут выполняться параллельно. Эти функции реализует блок распределения микрокоманд. Он выбирает микрокоманды из очереди не в порядке их поступления, а по мере готовности соответствующих операндов

и исполнительных устройств. В результате команды, поступившие позже, могут быть выполнены до ранее выбранных команд. При этом реализуется одновременное выполнение нескольких микрокоманд (команд) в параллельно работающих исполнительных устройствах. Таким образом, естественный порядок следования команд (микрокоманд) нарушается, чтобы обеспечить более полную загрузку параллельно включенных исполнительных устройств и повысить производительность процессора.

Адреса операндов, выбираемых из памяти, вычисляются блоком формирования адреса (БФА), который реализует интерфейс с кэш-памятью данных 1-го уровня. В соответствии с заданными в декодированных командах способами адресации формируются 48 адресов для загрузки операндов из памяти в регистр БРЗ и 24 адреса для записи из регистра в память (в Pentium III формируются 16 адресов для загрузки регистров и 12 адресов для записи в память). При этом БФА формирует адреса операндов для команд, которые еще не поступили на выполнение. При обращении к памяти БФА одновременно выдает адреса двух операндов: один для загрузки операнда в заданный регистр БРЗ, второй - для пересылки результата из БРЗ в память. Таким образом реализуется процедура предварительного чтения данных для последующей их обработки в исполнительных блоках (спекулятивная выборка).

Аналогичным образом организуется параллельная работа блоков SSE, FPU, MMX, которые используют отдельный набор регистров и блок формирования адресов операндов.

При выборке операнда из памяти производится обращение к кэшпамяти данных (L1), которая имеет отдельные порты для чтения и записи. За один такт производится выборка операндов для двух команд.

При формировании адресов обеспечивается обращение к заданному сегменту памяти. Каждый сегмент может делиться на страницы. Для сокращения времени трансляции используется **буфер ассоциативной трансляции страничного адреса** TLB, который хранит базовые адреса наиболее часто используемых страниц.

Микрокоманды поступают в исполнительное ядро из блока распределения по 4 портам в 8 исполнительных блоков. Эти порты выполняют функцию шлюзов к функциональным устройствам. Для обработки целочисленных данных и выполнения логических операций в Pentium 4 используются 4 однотипных арифметико-логических устройства (ALU). Обработка чисел с плавающей запятой проходит в FPU. Блоки ММХ и SSE предназначены для выполнения команд этих типов.

За один такт через порты может пройти до шести микрокоманд. Это больше, чем может выполнить препроцессор (3 микрокоманды за такт), что дает некоторую свободу в случае резкого увеличения количества готовых к исполнению микрокоманд. Суперскалярная архитектура микропроцессора реали-

зуется путем организации исполнительного ядра МП в виде ряда параллельно работающих блоков.

Арифметико-логические блоки ALU производят обработку целочисленных операндов, которые поступают из заданных регистров БРЗ. В эти же регистры заносится и результат операции. При этом проверяются условия ветвления для команд условных переходов и выдаются сигналы перезагрузки конвейера команд в случае неправильно предсказанного ветвления. Рабочая тактовая частота модулей ALU в два раза выше тактовой частоты процессора. Это достигается за счет срабатывания как по переднему, так и по заднему фронтам задающего тактового сигнала. Таким образом, каждый ALU-модуль способен выполнить до двух целочисленных операций за один рабочий такт процессора.

Эффективность конвейера резко снижается из-за необходимости его перезагрузки при выполнении условных ветвлений, когда требуется произвести очистку всех предыдущих ступеней и выбрать команду из другой ветви программы. Чтобы сократить потери времени, связанные с перезагрузкой конвейера, используется улучшенный блок предсказания ветвлений. Его основной частью является ассоциативная память, называемая буфером адресов ветвлений ВТВ, в которой хранятся 4092 адреса ранее выполненных переходов. Отметим, что в ВТВ процессора Pentium III хранятся адреса только 512 переходов. Кроме того, ВТВ содержит биты, хранящие предысторию ветвления, которые указывают, выполнялся ли переход при предыдущих выборках данной команды. При поступлении очередной команды условного перехода указанный в ней адрес сравнивается с содержимым ВТВ. Если этот адрес не содержится в ВТВ, то есть ранее не производились переходы по данному адресу, то предсказывается отсутствие ветвления. В этом случае продолжается выборка и декодирование команд, следующих за командой перехода. При совпадении указанного в команде адреса перехода с каким-либо из адресов, хранящихся в ВТВ, производится анализ предыстории. В процессе анализа определяется чаще всего реализуемое направление ветвления, а также выявляются чередующиеся переходы. Если предсказывается выполнение ветвления, то выбирается и загружается в конвейер команда, размещенная по предсказанному адресу. Более совершенный механизм предсказания переходов в МП Pentium 4 обеспечивает уменьшение количества ошибочно предсказанных переходов в среднем на 33 % по сравнению с Pentium III. Таким образом, резко уменьшается число перезагрузок конвейера при неправильном предсказании ветвления.

В Pentium 4 также интегрирован набор из 144 новых SIMD-инструкций, обеспечивающих одновременное выполнение одной операции над несколькими операндами. Рассмотрим особенности использования этой схемы обработки данных подробнее.

Технология MMX - итог совместной работы создателей архитектуры микропроцессоров INTel и программистов. При ее разработке был исследован ши-

рокий круг программ аудиовизуальной обработки информации: обработка изображений, MPEG-видео, синтеза музыки, сжатия речи и ее распознавания, поддержка видеоконференций, компьютерные игровые программы и т. д. В результате этого анализа были выявлены основные особенности таких программ:

- использование данных целого типа небольшой разрядности, например, 8-разрядные графические пиксели и 16-разрядная оцифровка звука;

- короткие циклы с высокими коэффициентами повторяемости;

- большое количество операций умножения и суммирования, в том числе из-за широкого использования быстрого преобразования Фурье;

- применение алгоритмов, требующих интенсивных вычислений;

- широкое использование операций с высоким уровнем параллелизма.

Было отмечено, что в мультимедийных приложениях 80 % времени выполнения программы приходится на 10-20 % программного кода.

Малая разрядность данных требует дополнительных действий при их обработке на 32-разрядном микропроцессоре, не позволяя в то же время использовать всю мощь 32-разрядной архитектуры.

Простым и наглядным примером такого рода обработки может служить изменение значений всех пикселей видеопамяти на определенную величину. Пусть емкость видеопамяти составляет 1 Мбайт, а каждый пиксель кодируется 1 байтом. Тогда для выполнения указанного действия потребуется выполнить примерно 1 млн операций по прибавлению константы к однобайтовому операнду, который выбирается из памяти. Одновременное выполнение таких действий над 4 операндами, что сократило бы количество операций в 4 раза, невозможно в классической архитектуре IA-32 из-за отсутствия соответствующих команд в системе команд и форматов используемых данных.

На устранение этих противоречий и были направлены основные усилия разработчиков технологии ММХ. Процессор Pentium MMX, в котором впервые была реализована новая технология, был представлен фирмой INTel в январе 1997 года. Он позволил на 10-20 % повысить производительность на стандартных тестах, а для специализированных мультимедийных приложений на 50 %.

### Тема 1.4 Микроконтроллеры (МК). Общие сведения

1. Классификация. Архитектура. Обобщенная структурная схема микроконтроллера серии AVR. Основные элементы структурной схемы. Назначение. Характеристика. Логические основы построения микроконтроллеров; классификацию устройств памяти систему команд.

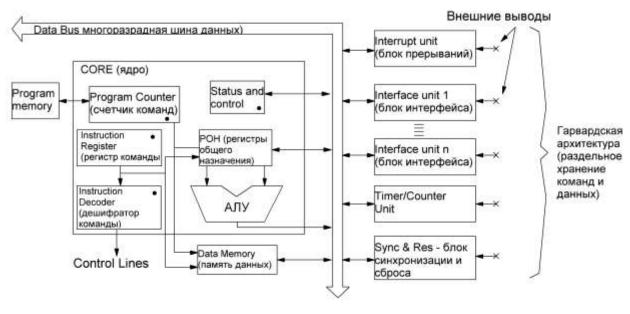

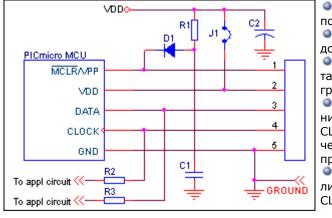

Рис.4

• -устройство управления, остальное – операционная часть.

## На примере МК AVR:

#### Процессор

ядро - ЦПУ, построенное на принципах RISK-архитектуры. Основа этого блока — АЛУ).По системному тактовому сигналу из памяти программ в соответствии с содержимым счетчика команд (PC) выбирается очередная команда и выполняется АЛУ. Во время выбора команды из памяти программ происходит выполнение предыдущей выбранной команды, что и позволяет достичь быстродействия. АЛУ подключено к POH (GPR). Регистров общего назначения всего 32, они имеют байтовый формат.

#### Память

В МК AVR реализована Гарвардская архитектура, по кот.с которой разделены не только адресные пространства памяти программ и памяти данных, но и шины доступа к ним. Каждая из областей памяти данных (RAM и EEPROM) также расположена в своем адресном пространстве. Память программ (Flash ROM или Flash ПЗУ)

Память программ предназначена для хранения последовательности команд, управляющих функционированием микроконтроллера, и имеет 16-ти битную организацию. Все AVR имеют Flash-память программ, которая может быть различного размера - от 1 до 256 КБайт. Ее главное достоинство в том, что она построена на принципе электрической перепрограммируемости. Программа заносится во Flash-память AVR как с помощью обычного программатора, так и с помощью SPI-интерфейса.

#### Память данных

Память данных разделена на три части: регистровая память, оперативная память (ОЗУ или RAM) и энергонезависимая память (ЭСППЗУ или EEPROM).

#### Регистровая память (РОН и РВВ)

Регистровая память включает 32 регистра общего назначения (РОН или GPR), объединенных в файл, и служебные регистры ввода/вывода (РВВ). И те и другие расположены в адресном пространстве ОЗУ, но не являются его частью.В области РВВ расположены различные служебные регистры (регистры управления микроконтроллером, регистры состояния и т. п.), а также регистры управления периферийными устройствами, входящими в состав микроконтроллера. По сути, управление микроконтроллером заключается в управлении этими регистрами.

#### Энергонезависимая память данных (EEPROM)

Для долговременного хранения различной информации, которая может изменяться в процессе функционирования микроконтроллерной системы, используется EEPROM-память. Этот тип памяти удобен для хранения промежуточных данных, различных констант, коэффициентов, серийных номеров, ключей и т.п.

#### Оперативная память (ОЗУ или RAM)

Используется для оперативного хранения данных. Число циклов чтения и записи в RAM не ограничено, но при отключении питающего напряжения вся информация теряется.

### Периферия

Периферия МК AVR включает: порты, поддержку внешних прерываний, таймеры-счетчики, сторожевой таймер, аналоговые компараторы, 10-разрядный 8-канальный АЦП, интерфейсы UART, JTAG и SPI, устройство сброса по понижению питания, широтно-импульсные модуляторы.

## Таймеры/счетчики (TIMER/COUNTERS)

Микроконтроллеры AVR имеют в своем составе от 1 до 4 таймеров/счетчиков (T/C) с разрядностью 8 или 16 бит, которые могут работать и как таймеры от внутреннего источника тактовой частоты, и как счетчики внешних событий. Их можно использовать для точного формирования временных интервалов, подсчета импульсов на выводах МК, формирования последовательности импульсов, тактирования приемопередатчика последовательного канала связи. В режиме ШИМ (PWM) T/C - широтно-импульсный модулятор и используется для генерирования сигнала с программируемыми частотой и скважностью. Т/С способны вырабатывать запросы прерываний.

Сторожевой таймер (WDT) Сторожевой таймер (WatchDogTimer) предназначен для предотвращения катастрофических последствий от случайных сбоев программы. Он имеет свой собственный RC-генератор, работающий на частоте 1 МГц

**Аналого-цифровой преобразователь (A/D CONVERTER)** Аналогоцифровой преобразователь (АЦП) служит для получения числового значения напряжения, поданного на его вход. Этот результат сохраняется в регистре данных АЦП. входом АЦП, определяется числом, занесенным в соответствующий регистр.

Универсальный последовательный приемопередатчик (UART или USART) Универсальный асинхронный или синхронно/асинхронный приемопередатчик (UART или USART) - последовательный интерфейс для организации информационного канала обмена микроконтроллера с внешним миром. Способен работать в дуплексном режиме. Он поддерживает протокол стандарта RS-232, что дает возможность связываться с ПК.

**Последовательный периферийный трехпроводный интерфейс SPI** SPI (SerialPeripheralInterface) - для организации обмена данными между 2 устройствами. С его помощью может осуществляться обмен данными между микроконтроллером и различными устройствами, такими, как цифровые потенциометры, ЦАП/АЦП, FLASH-ПЗУ и др, а также между несколькими микроконтроллерами AVR. Также, через SPI может осуществляться программирование микроконтроллера.

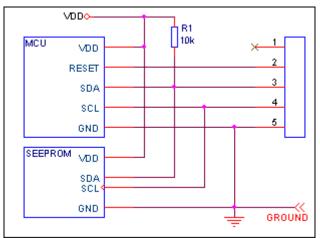

#### Двухпроводной последовательный интерфейс TWI

TWI (Two-wireSerialInterface) позволяет объединить вместе до 128 различных устройств с помощью двунаправленной шины, состоящей из линии тактового сигнала (SCL) и линии данных (SDA).

**Тактовый генератор** Тактовый генератор вырабатывает импульсы для синхронизации работы всех узлов микроконтроллера. Внутренний тактовый генератор AVR может запускаться от нескольких источников опорной частоты (внешний генератор, внешний кварцевый резонатор, внутренняя или внешняя RC-цепочка). Минимальная допустимая частота ничем не ограничена (вплоть до пошагового режима).

## Тема 1.5. Микроконтроллеры семейства серии AVR

1.Общие сведения. Архитектура. Регистры общего назначения (РОН). Регистры ввода — вывода. Память. Память программ и память данных. Счетчики команд и стековая память.

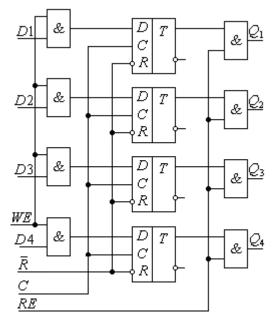

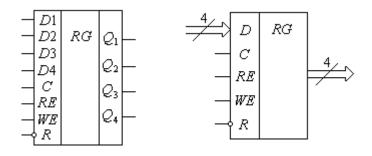

Регистры памяти – простейший вид регистров – хранят двоичную информацию. Это набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Если регистр построен на триггерах-защелках, то такой регистр называют регистром-защелкой. Схема такого регистра представлена на рис.4.

Типовыми внешними связями регистра являются информационные входы  $D_i$ , вход сигнала записи C (или загрузки синхронизации), вход гашения (установки в 0) R, выходы триггеров  $Q_i$ , разрешение выхода (чтения) RE, разрешение приема информации (записи) WE. Возможны другие обозначение информационных и управляющих входов и выходов. Условное изображение регистра показано на рис. 8.2.

Рис. 4. Регистр памяти

Изображение по варианту a используется, когда нужно показать каждый вход и выход данных. Если же тракт данных рассматривается как единое, укрупненное понятие — шина данных, то используется обозначение, показанное на рис. 5  $\delta$ .

а б

Рис. 5. Условное изображение регистра: a – с раздельными линиями по разрядам;  $\delta$  – с информационными линиями в виде шины

Часто регистры дополняются элементами отключения выходных шин. Тогда микросхема имеет дополнительный вход перевода в третье состояние EZ. Ввод (запись) и вывод (считывание) производится одновременно во всех разрядах при наличии разрешения WE или RE.

С приходом очередного тактового импульса происходит обновление информации. Считывание информации может осуществляться в однофазном виде в прямом или обратном коде (с выходов  $\overline{Q}$ ) или в парафазном виде.

В качестве подобных регистров могут быть использованы без дополнительных элементов многие синхронные триггеры: K155TM5, TM7, TM8, 564TM3, 555TM8 и др.

Наращивание разрядности регистра достигается добавлением нужного числа триггеров, тактовые входы которых присоединяют к линии синхронизации.

На рис. 6 представлен регистр К155ИР15 — регистр с тремя состояниями. Здесь D1-D4 — информационные входы, C — синхронизирующий вход. Запись осуществляется по фронту 0,1 ( $\Gamma$ ), $Q_1-Q_4$  — прямые выходы,  $E_1,E_2$  — разрешающие входы. Запись возможна при  $E_1=E_2=0$  (если на одном из входов E логическая 1, то это режим хранения информации). Входы  $EZ_1,EZ_2$  — перевод в 3-е состояние, R — установка в 0 (высоким уровнем): с приходом 1 на вход R все триггеры устанавливаются в 0. При вводе информации на входах  $E_1, E_2$  и R должен быть 0. Если на EZ (любом) логическая 1 — выходы отключаются. Более подробные сведения о режимах работы микросхемы можно посмотреть, например, в [12, 13].

Рис. 8.3. Цоколевка регистра К155ИР15

Рис. 6. Цоколевка регистра К155ИР15

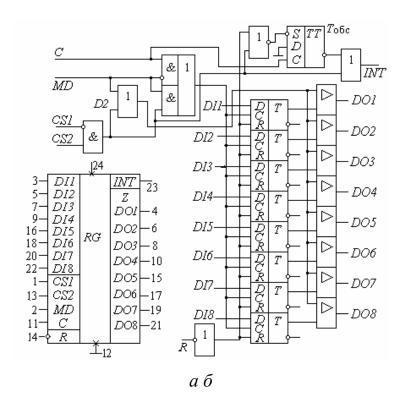

Выпускаемые промышленностью регистры иногда объединяют на кристалле микросхемы с другими узлами, в паре с которыми регистры часто используются в схемах цифровой аппаратуры. Пример такого комплексного узла — микросхема многорежимного буферного регистра K589 MP12. Условное обозначение и структура регистра представлены на рис. 7. Микросхема состоит из восьми информационных D-триггеров, восьми выходных буферных устройств с тремя состояниями, отдельного D-триггера для формирования запросов на прерывание и гибкой схемы управления режимами работы регистра.

Рис. 7. Условное обозначение (a) и функциональная схема ( $\delta$ ) регистра ИР12

Микросхема имеет 24 вывода, из которых шестнадцать служат для ввода входных данных – D11-D18 и вывода выходных данных – D01 - D08.

Управляющие сигналы: MD — выбор режима; CS1, CS2 — сигналы выбора кристалла; C — стробирующий сигнал; R — очистка (сброс); INT — сигнал прерывания, выдаваемый микропроцессору.

Запись информации в регистр обеспечивается одной из следующих комбинаций управляющих сигналов:  $CS1 \cdot CS2 \cdot MD$  у  $C \cdot MD$ , где CS1, CS2 — входы выборки кристалла; когда CS1=0 и CS2=1, регистр выбирается; С — вход для подачи стробирующего сигнала при записи; MD — вход выбора режима, используется для определения тактирующего сигнала на входе С триггеров регистра ( $CS1 \cdot CS2$  при MD=1 или C при MD=0) и для управления состоянием выходного буфера.

Чтение информации с регистра осуществляется одной из двух комбинаций входных сигналов: CS1, CS2 v MD. Формирование сигнала прерывания INT возможно при записи или чтении информации с регистра:  $CS1 \cdot CS2$  v C. Сброс запроса прерывания INT осуществляется сигналом очистки регистра R=0, или при  $CS1 \cdot CS2=1$  триггер прерывания устанавливается в 1.

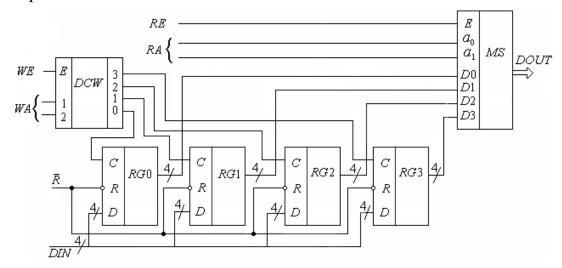

Часто регистры объединяются в блоки регистровой памяти — регистровые файлы. Такие микросхемы, могут быть объединены с входным дешифратором, позволяющим принимать входные данные в соответствующий регистр, выбираемый сигналами на адресных входах микросхемы. Объединяют регистры и с выходным мультиплексором MS, позволяющим выбирать содержи-

мое соответствующего регистра. Пример схемы такого устройства представлен на рис. 8.

Рис. 8. Схема регистра общего назначения

Входы  $D_i$  четырёх регистров подключены к общей входной шине данных DIN. Вход загрузки требуемого регистра выбирается дешифратором записи DCW на основании поступающего на вход DCW адреса записи WA (write address), т. е. кода номера загружаемого регистра. Запись данных, присутствующих на шине DIN, происходит по сигналу разрешения записи WE (write enable).

Выходы регистров мультиплексором MS подключаются к выходной шине DOUT (data out). Номер регистра, с которого происходит чтение, определяет код адреса чтения RA (read address). Выдачу данных в шину DOUT разрешает сигнал RE (read enable).

Поскольку дешифрация адреса записи и адреса чтения производится независимыми узлами (WA и RA), регистровая память может одновременно записывать данные в один регистр и читать из другого.

Описанная структура использована в микросхеме 155РП1. Аналогичные, но более развитые структуры имеют регистровые памяти ИР11 и ИР12 серий К561 и К564, ИР26 155 серии и др.

Микросхемы регистровой памяти легко наращиваются по разрядности и допускают наращивание по числу регистров. Они разработаны для построения блоков регистров общего назначения (РОН) и других специализированных блоков памяти небольшого объема, предназначенных для временного хранения исходных данных и промежуточных результатов в цифровом устройстве.

Для памяти с большим числом регистров часто используют один дешифратор адреса и при записи и при чтении. Такую память называют *памятью с произвольным доступом* (по ЕСКД это RAM) – ОЗУ. В таких устройствах и ввод, и вывод данных часто осуществляется через одни и те же выводы корпуса микросхемы за счёт использования элементов с тремя состояниями. Пример реализации двунаправленной шины управления рассмотрен ранее (см. рис.

3.35, a). Здесь при наличии на входе Z сигнала низкого уровня (0) информация передается слева направо, при наличии высокого уровня — справа налево.

Микросхемы ОЗУ малой ёмкости есть в составе распространённых серий. Они имеют входы адреса  $(A_i)$ , данных  $(D_i)$ , режима W/R, выходы данных  $Q_i$ , вход разрешения E (BM, BK, CS – выбор кристалла).

Примеры микросхем ОЗУ:

```

155РУ2 — 16*4 (16 слов по 4 разряда); 155РУ5 — 256*1; 564РУ2 — 256*1.

```

Это статические ОЗУ. Они более быстродействующие, чем динамические

2. Периферия микроконтроллера. Подсистема ввода — вывода. Система прерываний. Таймеры-счетчики, сторожевой таймер. Другие встроенные периферийные устройства. Основные понятия. Аналоговые компараторы (Analog Comparator). Аналого-цифровой преобразователь - АЦП (A/D CONVERTER). Интерфейсы. Универсальный последовательный асинхронный приемопередатчик (UART / USART) Интерфейсы UART. Последовательный периферийный интерфейс (SPI.). Последовательный двухпроводный интерфейс (TWI). Другие ячейки.

Регистровый файл SRAMзанимает младшие 32 байта в общем адресном пространстве ОМК. Шесть из 32-х регистров файла могут использоваться как три 16-разрядных указателя адреса при косвенной адресации данных. Один из этих указателей (Z Pointer) применяется также для доступа к данным, записанным в памяти программ микроконтроллера. Использование трех 16-битных указателей (X, Y и Z Pointers) существенно повышает скорость пересылки данных при работе прикладных программ.

Память программ. Все AVR- МК имеют Flash-память программ, которая может быть загружена как с помощью обычного программатора в параллельном формате, так и с помощью SPI- интерфейса, в том числе непосредственно на плате. Число циклов перезаписи — не менее 1000. Некоторые версии МК Меда имеют возможность самопрограммирования, т.е. микроконтроллер способен самостоятельно, без внешнего программатора, изменять содержимое ячеек памяти программ. Это дает возможность записать во внешнюю энергонезависимую память несколько рабочих версий программы, а потом при необходимости или по реакции на логические условия перегружать рабочие программы в тот же микроконтроллер AVR без извлечения его из печатной платы. Для этого весь массив памяти программ делится на две неравные по объему области: блок загрузчика (программа, которая управляет перезаписью Flash-памяти программ) и блок для размещения рабочих программ. Программа- загрузчик создается разработчиком и должна быть запрограммирована внешним программатором.

Память данных. Все AVR- МК имеют энергонезависимую память данных с

электрическим стиранием EEPROM. Этот тип памяти используется для хранения промежуточных данных, констант, таблиц перекодировок, калибровочных коэффициентов и т.п. Данные в EEPROM могут быть загружены как через SPI- интерфейс, так и с помощью обычного программатора. Число циклов перезаписи — не меньше 100 000. Два программируемых бита защиты информации позволяют защитить память программ и энергонезависимую память данных EEPROM от несанкционированного считывания.

Внутренняя оперативная память SRAM есть во всех AVR семейств Classic и Mega и в новом кристалле семейства Tiny – ATtiny26/L. Для некоторых МК возможно подключение внешней памяти данных объемом до 64 Кбайт.

Число независимых линий портов ввода/ вывода — от 3 до 53. Каждый разряд порта может быть запрограммирован на ввод или вывод информации. Мощные выходные драйверы обеспечивают токовую нагрузочную возможность 20 мА по линии порта при максимальном значении 40 мА. Общая токовая нагрузка на все линии одного порта не должна превышать 80 мА (для Vdd = 5 В).

Любой микроконтроллер AVR обязательно содержит набор периферийных устройств. Периферийные они по отношению к центральному процессорному устройству (ЦПУ) микроконтроллера. Но находятся они также внутри микросхемы. Ниже перечислены все возможные периферийные устройства, которые могут входить в состав микроконтроллера AVR.

Встроенные таймеры/счетчики.

Микроконтроллеры AVR могут содержать от одного до четырех таймеров/счетчиков. Причем используются как восьми-, так и шестнадцатиразрядные таймеры. Их количество на один микроконтроллер может составлять от одного до шести.

Генератор сигнала с широтно-импульсной модуляцией (ШИМ). Генерация сигнала ШИМ — это один из режимов работы таймера/счетчика. Одна микросхема может иметь от 2 до 12 каналов ШИМ, а может не иметь ни одного.

Аналоговый компаратор.

Входит в состав практически всех микроконтроллеров AVR.

Аналогово-цифровой преобразователь (АЦП). АЦП микроконтроллеров AVR могут иметь от четырех до шестнадцати каналов. То есть могут преобразовывать в цифровой эквивалент до 16 входных аналоговых сигналов. На самом деле канал АЦП всегда один. Но на его входе стоит аналоговый мультиплексор. Поэтому АЦП способен подключаться к нескольким разным источникам аналогового сигнала.

Последовательный интерфейс.

Микросхемы AVR способны поддерживать несколько разных видов последовательных интерфейсов. Каждый такой интерфейс реализует один или не-

сколько известных стандартов передачи информации. Один из видов такого интерфейса поддерживает тот же стандарт, что и СОМ-порт персонального компьютера. Есть также интерфейс, поддерживающий стандарт I2С шины. SPI-интерфейс может использоваться как для последовательного программирования памяти программ, так и для связи нескольких микроконтроллеров в мультипроцессорной системе.

Микроконтроллеры AVR содержат от 1 до 4 таймеров/счетчиков, которые могут работать как таймеры от внутреннего источника опорной частоты, и как счетчики внешних событий.

Таймер/счетчик RTC (есть во всех микроконтроллерах семейства Mega и в некоторых МК Classic) реализует систему реального времени. Таймер имеет собственный делитель, который может быть программным способом подключен или к основному внутреннему источнику тактовой частоты МК, или к дополнительному асинхронному источнику опорной частоты (кварцевый резонатор или внешний синхросигнал). Для этой цели МК имеет два внешних вывода. Внутренний осцилятор, нагруженный на счетный вход таймера/счетчика RTC, оптимизирован для работы с внешним "часовым" кварцевым резонатором на 32,768 кГц.

Блок SPI предназначен для последовательного ввода и вывода данных, также используется для программирования после установки МК на печатную плату.

Сторожевой таймер WDT служит для перезапуска программы при появлении сбоя в ходе ее выполнения. Программа, которая работает без сбоев, периодически сбрасывает сторожевой таймер, не допуская его переполнения. Сторожевой таймер имеет собственный RC-генератор, который работает на частоте 1 МГц. На входе WDT включен делитель с программируемым коэффициентом деления, позволяющий регулировать временной интервал переполнения таймера для сброса микроконтроллера. Таймер WDT может быть отключен программным способом во время работы микроконтроллера как в активном режиме, так и в любом из режимов пониженного энергопотребления. В последнем случае это приводит к значительному снижению потребляемого тока.

Аналоговый компаратор AC сравнивает по величине напряжения сигналы, поступающие на входы P1.0 и P1.1 Результат сравнения подается на внутреннюю линию, которая не имеет внешнего вывода.

Аналого-цифровой преобразователь ADC построен по схеме последовательного приближения с устройством выборки/хранения (УВХ). Каждый из аналоговых входов может быть соединен со входом УВХ через аналоговый мультиплексор. Устройство выборки/хранения имеет собственный усилитель. Разрядность АЦП — 10 бит при нормированной погрешности ± 2 МЗР. АЦП может работать в двух режимах — однократное преобразование по любому выбранному каналу и последовательный циклический опрос всех каналов. Время преобразования выбирается программно с помощью установки

коэффициента деления частоты специального предделителя, который входит в состав блока АЦП. Оно составляет от 60 до 280 мкс.

Внутренний тактовый генератор МК AVR может запускаться от нескольких источников опорной частоты (внешний генератор, внешний кварцевый резонатор, внутренняя или внешняя RC-цепочка). AVR-микроконтроллеры полностью статические — минимальная допустимая частота ничем не ограничена, т.е. возможно обеспечить даже пошаговый режим выполнения программы.

Микроконтроллеры AVR могут быть переведены программным путем в один из шести режимов пониженного энергопотребления:

- 1. Режим холостого хода (IDLE), в котором прекращает работу только процессор и фиксируется содержимое памяти данных, а внутренний генератор синхросигналов, таймеры, система прерываний и WDG-таймер продолжают функционировать.

- 2. Режим микропотребления (Power Down), при котором сохраняется содержимое регистрового файла, но останавливается внутренний генератор синхросигналов. Выход из Power Down возможен или по общему сбросу микроконтроллера, или по сигналу от внешнего источника прерывания. При включенном WDG-таймере ток потребления в этом режиме составляет около 80 мкА, а при выключенном меньше 1 мкА для всех типов AVR (для величины питающего напряжения 5 В).

- 3. Режим хранения энергии (Power Save), реализованный только в тех AVR, которые имеют в своем составе систему реального времени. В основном режим Power Save идентичен режиму Power Down, но он допускает независимую работу таймера/счетчика RTC. Выход из режима Power Save возможен по прерыванию, вызванному или переполнением таймера/счетчика RTC, или срабатыванием блока сравнения этого счетчика. Ток потребления в этом режиме составляет » 10 мкА при напряжении питания 5 В на частоте 32,768 кГц.

- 4. Режим подавления шума при работе аналого-цифрового преобразователя (ADC Noise Reduction). В этом режиме останавливается работа процессора, но разрешена работа АЦП, двухпроводного интерфейса I2C и сторожевого таймера.

- 5. Основной режим ожидания (Standby). Отличается от режима Power Down тем, что работа тактового генератора не прекращается. Это гарантирует быстрый выход микроконтроллера из режима ожидания всего за 6 тактов генератора.

- 6. Дополнительный режим ожидания (Extended Standby). Идентичный режиму Power Save, но работа тактового генератора тоже не прекращается, что гарантирует быстрый выход из режима за 6 тактов генератора.

Система команд AVRнасчитывает до 133 различных команд. Различают пять

групп команд AVR: условного разветвления, безусловного разветвления, арифметические и логические операции, команды пересылки данных, команды работы с битами. В последних AVR Меда реализована функция аппаратного умножения. По разнообразию и количеству команд AVR больше похожи на CISC-, чем на RISC-процессоры.

## Раздел 2 Алгоритмизация и программирование микроконтроллеров Тема 2.1 Языки программирования

1. Основные этапы эволюции языков программирования от машинных кодов и ассемблера до языков высокого уровня.

Обратимся к истокам развития вычислительной техники. Вспомним самые первые компьютеры и программы для них. Это была эра программирования непосредственно в машинных кодах, а основным носителем информации были перфокарты и перфоленты. Программисты обязаны были знать архитектуру машины досконально. Программы были достаточно простыми, что обуславливалось, во-первых, весьма ограниченными возможностями этих машин, и, во-вторых, большой сложностью разработки и, главное, отладки программ непосредственно на машинном языке. Вместе с тем такой способ разработки давал программисту просто невероятную власть над системой. Становилось возможным использование таких хитроумных алгоритмов и способов организации программ, какие и не снились современным разработчикам. Например, могла применяться (и применялась!) такая возможность, как самомодифицирующийся код. Знание двоичного представления команд позволяло иногда не хранить некоторые данные отдельно, а встраивать их в код как команды. И это далеко не полный список приемов, владение хотя бы одним из которых сейчас сразу же продвигает вас до уровня «гуру» экстракласса.

#### 2. Ассемблер

Первым значительным шагом представляется переход к языку ассемблера (позволим себе маленькое лирическое отступление: английское название assembly language, или assembler, на русский переводят именно тем термином, который был использован выше. При этом у новичка создается впечатление, что язык назван в честь некоего человека по имени ассемблер. Достаточно забавная ситуация, не правда ли?). Не очень заметный, казалось бы, шаг — переход к символическому кодированию машинных команд — имел на самом деле огромное значение. Программисту не надо было больше вникать в хитроумные способы кодирования команд на аппаратном уровне. Более того, зачастую одинаковые по сути команды кодировались совершенно различным образом в зависимости от своих параметров (широко известный пример из мира современных компьютеров — это кодирование инструкции моу в процессорах Intel: существует несколько совершенно по-разному кодируемых вариантов команды; выбор того или иного варианта зависит от операндов, хотя суть выполняемой операции неизменна: поместить содер-

жимое (или значение) второго операнда в первый). Появилась также возможность использования макросов и меток, что также упрощало создание, модификацию и отладку программ. Появилось даже некое подобие переносимости — существовала возможность разработки целого семейства машин со сходной системой команд и некоего общего ассемблера для них, при этом не было нужды обеспечивать двоичную совместимость.

Вместе с тем, переход к новому языку таил в себе и некоторые отрицательные (по крайней мере, на первый взгляд) стороны. Становилось почти невозможным использование всяческих хитроумных приемов сродни тем, что упомянуты выше. Кроме того, здесь впервые в истории развития программирования появились два представления программы: в исходных текстах и в откомпилированном виде. Сначала, пока ассемблеры только транслировали мнемоники в машинные коды, одно легко переводилось в другое и обратно, но затем, по мере появления таких возможностей, как метки и макросы, дизассемблирование становилось все более и более трудным делом. К концу ассемблерной эры возможность автоматической трансляции в обе стороны была утеряна окончательно. В связи с этим было разработано большой количество специальных программ-дизассемблеров, осуществляющих обратное преобразования, однако в большинстве случаев они с трудом могут разделить код и данные. Кроме того, вся логическая информация (имена переменных, меток и т.п.) теряется безвозвратно. В случае же задачи о декомпиляции языков высокого уровня примеры удовлетворительного решения проблемы и вовсе единичны.

2. Этапы разработки программы. Способы алгоритмизации и программирования работы микроконтроллеров

Разработка программ включает в себя следующие этапы:

- 1. Анализ и уточнение требований, предъявляемых к программе. Иногда этот этап называют постановкой задачи.

- 2. Проектирование алгоритма и выбор структур данных (или алгоритмизация).

- 3. Программирование и отладка.

- 4. Тестирование программы.

- 5. Документирование, подготовка инструкции для пользователя программы.

Первые два этапа являются определяющими этапами разработки программного обеспечения. Этап анализа и уточнения требований, предъявляемых к программе — необходимый и весьма ответственный этап, который осуществляется совместно пользователем (заказчиком) программы и ее разработчиком. На этом этапе на основе требований заказчика уточняются три основных момента:

• исходные данные программы: формат данных, источник и порядок ввода, объем исходных данных и ограничения на их значения;

- выходные данные программы: содержание, формат и порядок вывода, возможный объем исходных данных, заголовки и предполагаемые ограничения на их значения;

- аварийные ситуации при вводе и обработке данных и действия пользователя, предусматриваемые при их возникновении.

На этапе анализа и уточнения требований создается более полное, уточненное описание задачи, называемое спецификацией задачи. Спецификация задачи — это очень важный документ, который является техническим заданием на разработку программы и частью соглашения (договора) между разработчиком программного обеспечения и заказчиком.

В спецификации задачи выделяют две ее части:

- функциональную спецификацию;

- эксплуатационную спецификацию.

Функциональная спецификация описывает объекты, относящиеся к задаче: разбиение на предполагаемые подзадачи, их входные и выходные данные, связи между ними, реакции на аварийные ситуации.

Эксплуатационная спецификация содержит требования к скорости работы программы и используемым ресурсам памяти, характеристикам и конфигурации ЭВМ, на которой должна работать программа, и специальные требования к надежности и безопасности ее работы.

На втором этапе разработки программного обеспечения проектируется алгоритм решения задачи в соответствии с заданной спецификацией, формируется общая структура программы, определяются компоненты и их входные и выходные параметры.

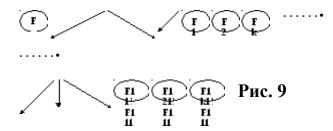

Основным подходом к проектированию структуры программы является нисходящее проектирование или пошаговое уточнение. Этот подход заключается в том, что программа первоначально рассматривается как «черный ящик», который выполняет некоторую функцию F, преобразующую единственные входные данные в единственные выходные данные. Это общая функция F может быть разделена на ряд более простых подфункций F1,F2,...,Fk. Каждая из этих функций сама по себе представляет такой же «черный ящик».

Процесс разбиения завершается тогда, когда любая из определенных функций может быть описана с помощью простых базовых операций и управляющих структур алгоритмов. В процессе проектирования формируется структура задачи в виде дерева подзадач (подфункций) (См. рис. 9).

Эта иерархическая структура задачи определяет структур компонент создаваемой программы. Компонента программы называется подпрограммой. В случае, если задача является сложной, целесообразно программу разделить на компоненты, одна из которых будет главной и организующей вычислительный процесс, а другие компоненты будут подпрограммами, которые будут выполняться в порядке, соответствующем алгоритму. Программы, выполняющие относительно простые задачи, могут не содержать подпрограмм.

Результатом данного этапа разработки является формализованное описание алгоритма или проект программы. Формы представления алгоритмов рассмотрены в п. 3.2.

Третьим этапом разработки программы является программирование и отладка. На этом этапе алгоритм записывается на языке программирования высокого уровня, и производится отладка программы с помощью соответствующей системы программирования (транслятора данного языка). Во время отладки исправляются обнаруженные в тексте программы ошибки. Результатом отладки является текст программы, не содержащей ошибок и выполненной хотя бы один раз на ПЭВМ. Таким образом, создается работоспособная программа.

На этапе тестирования программы выполняется проверка правильности работы программы с использованием заранее подготовленных тестов. Тест — это набор исходных данных и соответствующих им результатов, которые должна выдавать программа при обработке этих исходных данных. Для сложных задач составление тестов является весьма трудоемкой работой, включающей ручные расчеты или использование других программ-аналогов.

При обнаружении неправильных результатов на этапе тестирования происходит возврат на предыдущие этапы разработки программы. Результатом тестирования является окончательная версия программы и документация о результатах выполнения тестов.